## THÈSE DE DOCTORAT

de l'Université de recherche Paris Sciences et Lettres PSL Research University

# Préparée à l'École Normale Supérieure

Une Approche Combinée Langage-Polyédrique pour la Programmation Parallèle Hétérogène

A Combined Language and Polyhedral Approach for Heterogeneous Parallelism

## Ecole doctorale n°386

École doctorale de Sciences Mathématiques de Paris Centre

Spécialité Informatique

Soutenue par Jie ZHAO le 13 décembre 2018

Dirigée par Albert COHEN

### **COMPOSITION DU JURY:**

Mme. HALL Mary W. University of Utah, Rapporteur

M. BASTOUL Cédric Université de Strasbourg, Rapporteur

M. MCCOLL Bill Huawei/University of Oxford, Examinateur

M. ZAPPA NARDELLI Francesco ENS Paris/INRIA, Examinateur

M. TADONKI Claude Mines ParisTech/CRI, Examinateur

M. COHEN Albert Google/INRIA, Directeur de these

# Acknowledgements

To be honest, I had always been doubting about the impressive performance and the surprising magic of the polyhedral model before I joined the PARKAS group. The obscure mathematical abstractions of the model always prevented me from getting to the bottom of the polyhedral world. I therefore came to a decision to go into this world by pursuing a PhD degree majoring this research direction. Today, I eventually reach the end of this path, with the guidance, advices, supports and assistances from a large number of persons to name.

I would like to show my foremost gratefulness to my supervisor, Albert Cohen, for leading me the way to the world of polyhedral compilation and being patient, keen and passionate to help me dig into practical and interesting research ideas. Albert always provided me very valuable feedbacks via in-person discussions and online exchanges of views, leaving me much freedom and space to explore the issues and seek solutions independently. He also gave me plenty of guidance and loads of suggestions with his forward-looking insight, inspiring me to follow the promising research directions in academy and up-and-coming industry issues. It was a great experience advised by Albert and I cannot wait to work with him again.

Many thanks to Michael Kruse, Oleksandr Zinenko, Chandan Reddy and Riyadh Baghdadi for the interesting and helpful conversations during my doctoral study. Talking with them helps me better understand the mathematical background of polyhedral compilation and their constructive suggestions on my work always help me make progress. Thanks to Marc Pouzet, Francesco Zappa Nardelli and Timothy Bourke for leading the PARKAS team and establishing a harmonious environment for the smooth progress of my thesis. I also acknowledge Ulysse Beaugnon, Lélio Brun, and Guillaume Iooss, who helped me a lot on my registration in the doctoral school and the university as well as many other daily activities.

I would also like to acknowledge Bill McColl and his team, including Chong Li, Zhen Zhang, Sheng Yang, and Yu Xia, for hosting me during my visit at Huawei Research at Paris. We have evolved good friendships and they will last for my whole life. The collaboration work at Huawei for building a connected, intelligent world is an unforgettable experience. Thanks to your support and grant for my visit to the Huawei Research Center at Beijing, China. I am expecting to cooperate with you in the future.

I am very grateful to the valuable time and efforts from the reviewers of my PhD dissertation,

#### Acknowledgements

Mary W. Hall and Cédric Bastol. Thanks to Mary W. Hall for the help to a better comprehension about sparse computations, with an in-depth look into your approach and the NVIDIA implementations of the applications. Thanks to the practical comments and criticisms from Cédric Bastol for helping improve the quality of this work.

I also feel very thankful to the contributors of the PPCG code generator and the isl integer solving library, Sven Verdoolaege and Tobias Grosser. This work would not be possible without the contributions of their work. I would also like to acknowledge the contributors and developers of a large number of underlying components of polyhedral compilers and optimizers, including pet, Pluto, CLooG, Omega, iscc, etc., without which the understanding of the polyhedral model would be an unimaginable task.

I have to express my deep gratefulness to some important persons who walked with me the path of undergraduate and graduate study, including Baoliang Li, Jinchen Xu, Zhifeng Chen, Guanghui Liang and Xu Zhao, without some of whom my programming knowledge and skills would be impossible.

Last but not least, I want to acknowledge my family for their endless support to my education from the childhood. Everyone needs a house to live in, but a supportive family is what builds a home.

Paris, 10 December 2018

Jie Zhao

## Remerciements

Pour être honnête, j'ai toujours douté des performances impressionnantes et de la magie surprenante du modèle polyédrique avant de rejoindre le groupe PARKAS. Les obscures abstractions mathématiques du modèle m'ont toujours empêché d'atteindre le fond du monde polyédrique. J'ai donc pris la décision d'entrer dans ce monde en poursuivant un doctorat dans le domaine de la recherche. Aujourd'hui, J'arrive finalement au bout de ce chemin, avec les conseils, les soutiens et les assistances d'un grand nombre de personnes.

Je tiens à exprimer ma plus profonde gratitude à mon superviseur, Albert Cohen, pour m'avoir conduit au monde de la compilation polyédrique et pour sa patience, sa volonté et sa passion pour m'aider à approfondir des idées de recherche pratiques et intéressantes. Albert m'a toujours fourni des retours très utiles via des discussions en personne et des échanges de vues en ligne, me laissant ainsi beaucoup de liberté et d'espace pour explorer les problèmes et rechercher des solutions de manière autonome. Il m'a également donné beaucoup de conseils et une foule de suggestions grâce à sa vision prospective, m'inspirant de suivre les orientations de recherche prometteuses dans le monde académique et les questions d'actualité. Ce fut une excellente expérience conseillée par Albert et je suis impatient de retravailler avec lui.

Un grand merci à Michael Kruse, à Oleksandr Zinenko, à Chandan Reddy et à Riyadh Baghdadi pour les conversations intéressantes et utiles que j'ai eues au cours de mon doctorat. Parler avec eux m'aide à mieux comprendre le contexte mathématique de la compilation polyédrique et leurs suggestions constructives sur mon travail m'aident toujours à progresser. Merci à Marc Pouzet, Francesco Zappa Nardelli et Timothy Bourke d'avoir dirigé l'équipe de PARKAS et créé un environnement harmonieux pour le bon déroulement de ma thèse. Je tiens également à remercier Ulysse Beaugnon, Lélio Brun et Guillaume Iooss, qui m'ont beaucoup aidé lors de mon inscription à l'école doctorale et à l'université ainsi que de nombreux autres travaux quotidiens.

Je tiens également à remercier Bill McColl et son équipe, notamment Chong Li, Zhen Zhang, Sheng Yang et Yu Xia, de m'avoir accueilli lors de ma visite à Huawei Research à Paris. Nous avons développé de bonnes amitiés et elles dureront toute ma vie. La collaboration chez Huawei pour créer un monde connecté et intelligent est une expérience inoubliable. Merci pour votre soutien et votre subvention pour ma visite au centre de recherche Huawei à Pékin, en Chine. Je compte coopérer avec vous à l'avenir.

### Acknowledgements

Je suis très reconnaissant au temps précieux et aux efforts des rapporteurs de ma thèse, Mary W. Hall et Cédric Bastol. Merci à Mary W. Hall pour l'aide à une meilleure compréhension des calculs clairsemés, avec un examen approfondi de votre approche et des implémentations NVIDIA des applications. Merci aux commentaires pratiques et aux critiques de Cédric Bastol pour avoir aidé à améliorer la qualité de ce travail.

Je suis également très reconnaissant aux contributeurs du générateur de code PPCG et de la bibliothèque de résolution intégrale d'isl, Sven Verdoolaege et Tobias Grosser. Ce travail ne serait pas possible sans les contributions de leur travail. J'aimerais également remercier les contributeurs et les développeurs d'un grand nombre de composants sous-jacents de compilateurs et optimiseurs polyédriques, y compris pet, Pluto, CLooG, Omega, iscc, etc., sans lesquels la compréhension du modèle polyhédral serait une tâche inimaginable.

Je dois exprimer ma profonde gratitude à certaines personnes importantes qui ont suivi avec moi le chemin des études de premier et deuxième cycles, notamment Baoliang Li, Jinchen Xu, Zhifeng Chen, Guanghui Liang et Xu Zhao, sans lesquelles mes connaissances et mes compétences en programmation seraient impossible.

Enfin, je tiens à remercier ma famille pour son soutien sans faille à mon éducation dès mon enfance. Tout le monde a besoin d'une maison, mais c'est une famille qui apporte son soutien qui construit une maison.

A Paris, le 10 décembre 2018

Jie Zhao

## **Abstract**

After a thirty-year history of development, the polyhedral model has evolved into a powerful solution to exploiting automatic parallelization and locality optimization. As bridging software between the high-level description of programs and the underlying implementation of hardware, polyhedral compilation is increasingly challenged by the diversity of programming languages and heterogeneity of architectures. A long standing limitation of the model has been its restriction to static control affine programs, resulting in an emergent demand for the support of non-affine extensions. This is particularly acute in the context of heterogeneous architectures where a variety of computation kernels need to be analyzed and transformed to match the constraints of hardware accelerators and to manage data transfers across memory spaces.

We explore multiple non-affine extensions of the polyhedral model, in the context of a well-defined intermediate language combining affine and syntactic elements. The thesis is organized as follows.

In the first part, we explain the challenges faced by the polyhedral model with respect to programming languages and architectures, and provide a brief introduction to polyhedral compilation.

In the second part, we present a method to parallelize and optimize loop nests for an important class of programs where counted loops have a dynamic data-dependent upper bound. Such loops are amenable to a wider set of transformations than general while loops with inductively defined termination conditions: for example, the substitution of closed forms for induction variables remains applicable, removing the loop-carried data dependences induced by termination conditions.

Our approach relies on affine relations only, as implemented in state-of-the-art polyhedral libraries. Revisiting a state-of-the-art framework to parallelize arbitrary while loops, we introduce additional control dependences on data-dependent predicates. Our method goes beyond the state of the art in fully automating the process, specializing the code generation algorithm to the case of dynamic counted loops and avoiding the introduction of spurious loop-carried dependences. We conduct experiments on representative irregular computations, from dynamic programming, computer vision and finite element methods to sparse matrix linear algebra. We validate that the method is applicable to general affine transformations for

locality optimization, vectorization and parallelization.

In the third part, we propose an automatic implementation of non-affine transformations by revisiting overlapped tiling in polyhedral compilation. Polyhedral frameworks implement classical forms of rectangular/parallelogram tiling affine transformations, but these forms lead to pipelined start and rather inefficient wavefront parallelism. Some experimental branches of existing polyhedral compilers evaluated sophisticated shapes such as trapezoid or diamond tiles, enabling concurrent start along the axes of the iteration space, but leading to custom scheduling and code generation methods insufficiently integrated with the general framework. Overlapped tiling is a technique designed to eliminate pipelined start by modifying tile shapes obtained from existing frameworks, but no implementations in a general-purpose polyhedral framework has been available until now, preventing its application in general-purpose loopnest optimizers and hampering the fair comparison with other techniques.

We revisit overlapped tiling in polyhedral compilation and demonstrate how to derive tighter tile shapes with less redundant computations, by enabling overlapped tiles in a schedule-tree-based algorithm. Our method allows the generation of both acute and right trapezoid shapes. It goes beyond the state of the art by avoiding the restriction to a domain-specific language or introducing post-pass rescheduling and custom code generation. We conduct experiments on the PolyMage benchmarks and representative iterated stencils, validating the effectiveness and general applicability of our technique on both general-purpose multicores and accelerators.

Finally, we summarize our work and present concluding remarks as well as future research directions. We believe the contributions collected in this dissertation extend the reach fof the polyhedral model to wider ranges of real-world programs. We also believe this work contributes to the integration of polyhedral methods with other compilation techniques.

## Résumé

Après trente ans de développement, le modèle polyédrique est devenu une solution puissante pour exploiter la parallélisation automatique et l'optimisation de la localisation. En tant que logiciel de transition entre la description de haut niveau des programmes et la mise en œuvre sous-jacente du matériel, la compilation polyédrique est de plus en plus remise en cause par la diversité des langages de programmation et l'hétérogénéité des architectures. Un défaut de longue date du modèle est sa restriction aux programmes affines de contrôle statique, entraînant une demande émergente pour la prise en charge des extensions non affines, en particulier à l'ère des architectures hétérogènes.

Nous étudions les extensions non affines dans le modèle polyédrique en le combinant avec un langage intermédiaire bien défini. La thèse est organisée comme ci-dessous.

Dans la première partie, nous expliquons les défis rencontrés par le modèle polyédrique en ce qui concerne les langages de programmation et les architectures, et décrivons une brève introduction à la compilation polyédrique pour aider les lecteurs à comprendre le principe du travail.

Dans la seconde partie, nous présentons l'approche du traitement des applications non affines en étudiant la compilation parallélisante et l'optimisation d'imbrication en boucle d'une classe importante de programmes où les boucles comptées ont une limite supérieure dynamique dépendante des données. De telles boucles se prêtent à un ensemble de transformations plus large que les boucles générales while avec des conditions de terminaison inductives : par exemple, la substitution des formes fermées par les variables d'induction reste applicable, éliminant les dépendances induites par les conditions de terminaison. Nous proposons une méthode de compilation automatique pour paralléliser et optimiser les boucles comptées dynamiques.

Notre approche repose uniquement sur des relations affines, mises en œuvre dans des bibliothèques polyédriques à la pointe de la technologie. En revisitant un cadre de pointe pour paralléliser des boucles arbitraires while, nous introduisons des dépendances de contrôle supplémentaires sur les prédicats dépendant des données. Notre méthode va au-delà de l'état de la technique en automatisant complètement le processus, en spécialisant l'algorithme de génération de code au cas des boucles comptées dynamiques et en évitant l'introduction de dépendances parasites en boucle. Nous effectuons des expériences sur des calculs irréguliers

représentatifs, allant de la programmation dynamique, de la vision par ordinateur et des méthodes par éléments finis à l'algèbre linéaire à matrice fragmentée. Nous validons que la méthode est applicable aux transformations affines générales pour l'optimisation de la localité, la vectorisation et la parallélisation.

Dans la troisième partie, nous proposons une implémentation automatique des transformations non affines en revisitant les mosaïques superposées dans la compilation polyédrique. Les structures polyédriques mettent en œuvre des formes classiques de transformations affines de carrelage rectangulaire/parallélogramme, mais ces formes conduisent à un démarrage en pipeline et à un parallélisme de front d'onde plutôt inefficace. Certaines branches expérimentales de compilateurs polyédriques existants ont évalué des formes sophistiquées telles que des carreaux trapézoïdaux ou diamantés, permettant un démarrage simultané sur les axes de l'espace d'itération, mais conduisant à des méthodes de planification et de génération de code insuffisamment intégrées au cadre général. Le pavage superposé est une technique conçue pour éliminer le démarrage en pipeline en modifiant les formes de pavés obtenues à partir de structures existantes, mais aucune implémentation dans une structure polyédrique polyvalente n'était disponible jusqu'à présent, empêchant son application dans les optimiseurs de boucle comparaison avec d'autres techniques.

Nous revisitons les mosaïques superposées dans la compilation polyédrique et montrons comment obtenir des formes de mosaïques plus étroites avec des calculs moins redondants, en activant des mosaïques superposées dans un algorithme basé sur un calendrier. Notre méthode permet de générer des formes trapézoïdales aiguës et droites. Cela dépasse l'état de la technique en évitant la restriction à un langage spécifique à un domaine ou en introduisant une reprogrammation post-pass et une génération de code personnalisée. Nous effectuons des expériences sur les repères PolyMage et les gabarits itératifs représentatifs, validant ainsi l'efficacité et l'applicabilité générale de notre technique sur les multicœurs et les accélérateurs polyvalents.

Enfin, nous résumons notre travail et discutons de quelques remarques de conclusion pour les futures directions de recherche. Le travail de cette thèse met le modèle polyédrique en application dans des programmes réels, en étendant les champs applicables du modèle et en soutenant l'intégration avec d'autres algorithmes de compilation.

# **Contents**

| Ac | knov    | wledgements (English/Français)                              | iii |

|----|---------|-------------------------------------------------------------|-----|

| Ał | ostra   | ct (English/Français)                                       | vi  |

| Li | st of   | figures                                                     | xii |

| Li | st of   | tables                                                      | xv  |

| Pa | ırt I : | Introduction & Background                                   | 1   |

| 1  | Intı    | roduction                                                   | 3   |

|    | 1.1     | From General-purpose Languages to Domain-specific Languages | 4   |

|    | 1.2     | Architecture Diversity                                      | 5   |

|    | 1.3     | Beyond Parallelization and Locality Optimization            | 7   |

|    | 1.4     | Combining Languages and the Polyhedral Model                | 8   |

| 2  | Bac     | kground                                                     | 11  |

|    | 2.1     | Polyhedral Compilation                                      | 11  |

|    |         | 2.1.1 An Overview                                           | 12  |

|    |         | 2.1.2 Polyhedral Representations                            | 16  |

|    |         | 2.1.3 Loop Transformations                                  | 19  |

|    |         | 2.1.4 Schedule Trees                                        | 20  |

|    | 2.2     | A Platform-Neutral Compute Intermediate Language            | 22  |

| Pa | ırt II  | : Handling Non-affine Applications                          | 25  |

| 3  | Dyr     | namic Counted Loops                                         | 27  |

|    | 3.1     | Background and Motivation                                   | 27  |

|    |         | 3.1.1 Limitations of Previous Work                          | 28  |

|    |         | 3.1.2 Static Control Parts                                  | 29  |

|    |         | 3.1.3 Our Solution                                          | 30  |

|    | 3.2     | Extension Nodes in Schedule Trees                           | 30  |

|    | 3.3     | An Overview of Our Approach                                 | 31  |

|    | 3.4     | Related Work                                                | 33  |

### **Contents**

| 4  | Sch   | eduling Dynamic Counted Loops in the Polyhedral Model | 35 |  |  |  |  |

|----|-------|-------------------------------------------------------|----|--|--|--|--|

|    | 4.1   | Preparation                                           | 35 |  |  |  |  |

|    | 4.2   | Deriving a Static Upper Bound                         | 37 |  |  |  |  |

|    |       | 4.2.1 Static Approaches                               | 37 |  |  |  |  |

|    |       | 4.2.2 Dynamic Approaches                              | 38 |  |  |  |  |

|    | 4.3   | Modeling Control Dependences                          | 38 |  |  |  |  |

|    | 4.4   | Scheduling                                            | 39 |  |  |  |  |

|    |       | 4.4.1 Schedule Construction                           | 39 |  |  |  |  |

|    |       | 4.4.2 Schedule Transformation                         | 41 |  |  |  |  |

| 5  | Gen   | neration of Imperative Code                           | 45 |  |  |  |  |

|    | 5.1   | Extending the Schedule Tree                           | 45 |  |  |  |  |

|    | 5.2   | Generating Early Exits                                | 46 |  |  |  |  |

|    | 5.3   | Changing Back to Dynamic Conditions                   | 47 |  |  |  |  |

|    | 5.4   | Code Generation for a Single Loop                     | 48 |  |  |  |  |

|    | 5.5   | Flat and Nested Parallelisms                          | 49 |  |  |  |  |

|    |       | 5.5.1 Flat parallelism within a band                  | 50 |  |  |  |  |

|    |       | 5.5.2 Nested parallelism across bands                 | 52 |  |  |  |  |

|    | 5.6   | General Applicability to Loop Transformations         | 53 |  |  |  |  |

|    |       | 5.6.1 Loop Transformations of Unimodular Matrices     | 53 |  |  |  |  |

|    |       | 5.6.2 Loop Transformations in Code Generation         | 55 |  |  |  |  |

|    |       | 5.6.3 Other Loop Transformations                      | 56 |  |  |  |  |

| 6  | Exp   | erimental Results                                     | 57 |  |  |  |  |

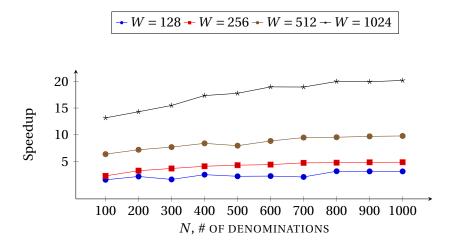

|    | 6.1   | Dynamic Programming                                   | 57 |  |  |  |  |

|    | 6.2   | HOG Benchmark                                         |    |  |  |  |  |

|    | 6.3   | Finite Element Method                                 | 60 |  |  |  |  |

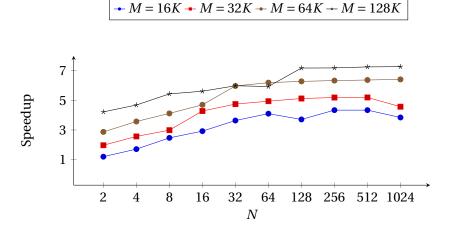

|    | 6.4   | Sparse Matrix-Vector Multiplication                   | 61 |  |  |  |  |

|    | 6.5   | Inspector/Executor                                    | 64 |  |  |  |  |

|    | 6.6   | Performance on CPU Architectures                      | 64 |  |  |  |  |

| Pa | rt II | I : Automating Non-affine Transformations             | 67 |  |  |  |  |

| 7  | Ove   | erlapped Tiling                                       | 69 |  |  |  |  |

|    | 7.1   | Background and Motivation                             | 70 |  |  |  |  |

|    |       | 7.1.1 Loop Tiling                                     | 70 |  |  |  |  |

|    |       | 7.1.2 Image Processing Pipelines                      | 71 |  |  |  |  |

|    |       | 7.1.3 Limitations of the Hyperplane-based Technique   | 72 |  |  |  |  |

|    |       | 7.1.4 Our solution                                    | 73 |  |  |  |  |

|    | 7.2   | Expansion Nodes in Schedule Trees                     | 73 |  |  |  |  |

|    | 73    | Related Work                                          | 74 |  |  |  |  |

| 8  | Acu    | te Trapezoid Tiling and Right Trapezoid Tiling | 77  |

|----|--------|------------------------------------------------|-----|

|    | 8.1    | Representations in Schedule Trees              | 77  |

|    | 8.2    | Acute Trapezoid Tiling                         | 78  |

|    | 8.3    | Right Trapezoid Tiling                         | 80  |

|    | 8.4    | Schedule Generation                            | 81  |

|    | 8.5    | Removal of Control Overheads                   | 82  |

|    | 8.6    | Comparing the Two Trapezoid Tile Shapes        | 83  |

|    | 8.7    | Handling Multi-statement/-dimensional Cases    | 85  |

|    |        | 8.7.1 Multiple Statements                      | 85  |

|    |        | 8.7.2 Multi-dimensional Statements             | 85  |

|    | 8.8    | Complementary Transformations                  | 86  |

|    |        | 8.8.1 Alignment and Scaling                    | 86  |

|    |        | 8.8.2 Fusion                                   | 86  |

|    |        | 8.8.3 Reducing Memory Footprint                | 87  |

|    |        | 8.8.4 Hybrid Tiling                            | 87  |

| 9  | Eval   | luations                                       | 89  |

|    | 9.1    | Experimental Setup                             | 89  |

|    | 9.2    | Image Processing Pipelines                     | 89  |

|    |        | 9.2.1 Bilateral Grid                           | 90  |

|    |        | 9.2.2 Camera Pipeline                          | 91  |

|    |        | 9.2.3 Harris Corner Detection                  | 92  |

|    |        | 9.2.4 Local Laplacian Filter                   | 93  |

|    |        | 9.2.5 Multiscale Interpolation                 | 94  |

|    |        | 9.2.6 Pyramid Blending                         | 94  |

|    |        | 9.2.7 Unsharp Mask                             | 95  |

|    | 9.3    | Iterated Stencils                              | 96  |

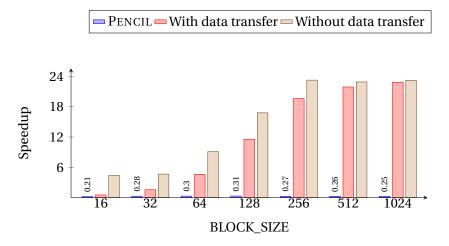

|    | 9.4    | Performance on GPU Architectures               | 98  |

| Pa | ırt IV | : Conclusions                                  | 101 |

| 10 | Con    | clusions and Perspectives                      | 103 |

|    | 10.1   | Conclusions                                    | 103 |

|    |        |                                                | 104 |

| Bi | bliog  | raphy                                          | 120 |

# **List of Figures**

| 1.1 | The trend of clock frequency and number of cores per chip in the past 50 years | 3  |

|-----|--------------------------------------------------------------------------------|----|

| 2.1 | A general workflow of polyhedral compilation                                   | 12 |

| 2.2 | 1D iterated stencil and its iteration space before and after scheduling        | 14 |

| 2.3 | An illustrative diagram on different code generation algorithms                | 16 |

| 2.4 | An illustrative loop nest and its iteration space in polyhedral compilation    | 18 |

| 2.5 | The schedule tree of the code in Figure 2.4(a)                                 | 22 |

| 2.6 | A high level overview of the Pencil compilation flow                           | 24 |

| 3.1 | Example with dynamic counted loops                                             | 29 |

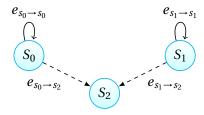

| 3.2 | Dependence graph of the example                                                | 32 |

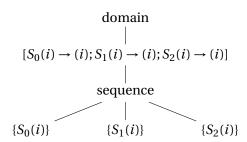

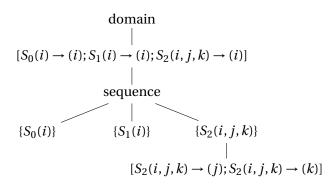

| 3.3 | Original schedule tree of the example                                          | 33 |

| 4.1 | A sparse matrix computation and its normalized format                          | 35 |

| 4.2 | A while loop and its normalized format                                         | 36 |

| 4.3 | Conditional abstraction                                                        | 39 |

| 4.4 | A correct schedule tree of the example                                         | 40 |

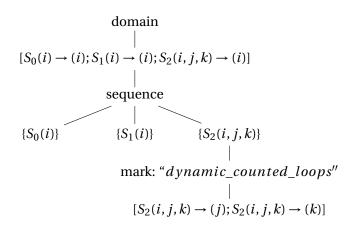

| 4.5 | Inserting mark nodes in the schedule tree                                      | 42 |

| 4.6 | Mark nodes with split band nodes                                               | 43 |

| 4.7 | Replace each mark node with an extension node                                  | 43 |

| 5.1 | Fusing two dynamic counted loops                                               | 48 |

| 5.2 | Code generation with loop tiling for CPU                                       | 49 |

| 5.3 | The schedule tree representation of code shown in Figure 5.2                   | 50 |

| 5.4 | An interchange example                                                         | 51 |

| 5.5 | Sinking the dynamic definition and its schedule tree representation            | 53 |

| 5.6 | Code generation with loop tiling for GPU                                       | 54 |

| 5.7 | The schedule tree representation of the code shown in Figure 5.6               | 55 |

| 6.1 | Performance of change-making on GPU                                            | 58 |

| 6.2 | Performance of the bucket sort on GPU                                          | 59 |

| 6.3 | Performance of the HOG descriptor on GPU                                       | 60 |

| 6.4 | Performance of equake on GPU                                                   | 61 |

| 6.5 | Performance of the CSR SpMV on GPU                                             | 63 |

## **List of Figures**

| 6.6  | Performance of the ELL SpMV on GPU                   | 64 |

|------|------------------------------------------------------|----|

| 6.7  | Performance of the HOG descriptor on CPU             | 65 |

| 6.8  | Performance of equake on CPU                         | 65 |

| 6.9  | Performance of the CSR SpMV on CPU                   | 66 |

| 6.10 | Performance of the ELL SpMV on CPU                   | 66 |

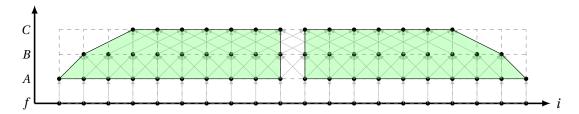

| 7.1  | Comparison of different tile shapes                  | 71 |

| 7.2  | A simple image processing pipeline                   | 72 |

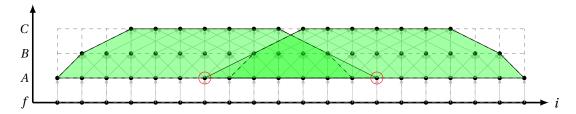

| 7.3  | Shaded regions of acute trapezoid tiling             | 72 |

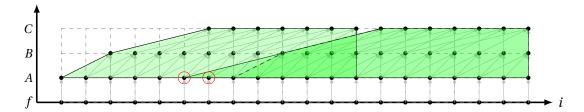

| 7.4  | Shaded regions of right trapezoid tiling             | 74 |

| 8.1  | The original schedule tree of the code in Figure 7.2 | 78 |

| 8.2  | Rectangular tiling regardless of the correctness     | 79 |

| 8.3  | Acute trapezoid tiling                               | 79 |

| 8.4  | Rectangular tiling after shifting                    | 80 |

| 8.5  | Right trapezoid tiling                               | 80 |

| 8.6  | Schedule tree of acute trapezoid tiling              | 81 |

| 8.7  | Schedule tree of right trapezoid tiling              | 81 |

| 8.8  | Code generated by acute trapezoid tiling             | 84 |

| 8.9  | Code generated by right trapezoid tiling             | 84 |

| 8.10 | Schedule tree of multiple statements                 | 85 |

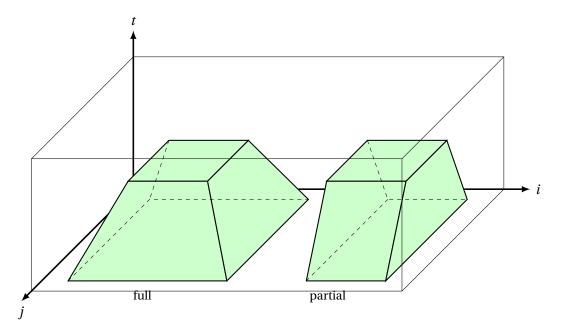

| 8.11 | Full and partial dimensional overlapped tiling       | 87 |

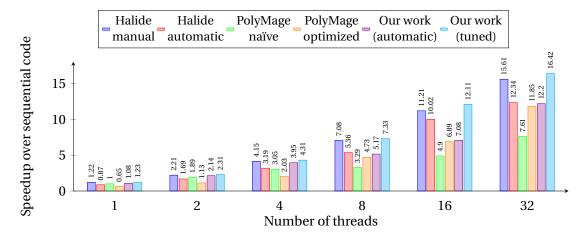

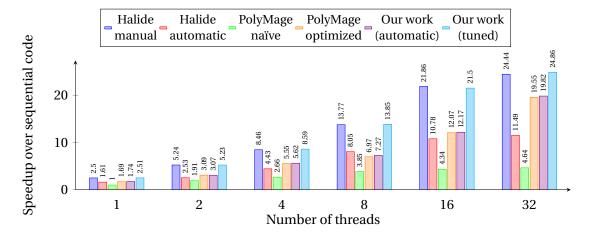

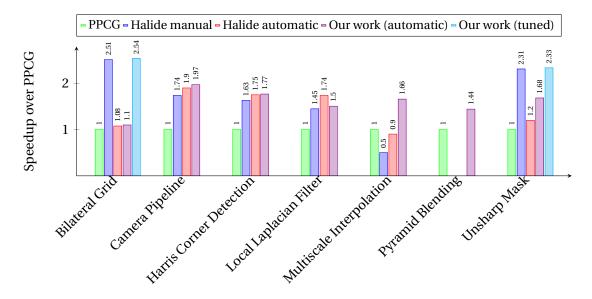

| 9.1  | Performance of Bilateral Grid on CPU                 | 91 |

| 9.2  | Performance of Camera Pipeline on CPU                | 92 |

| 9.3  | Performance of Harris Corner Detection on CPU        | 93 |

| 9.4  | Performance of Local Laplacian Filter on CPU         | 93 |

| 9.5  | Performance of Multiscale Interpolation on CPU       | 94 |

| 9.6  | Performance of Pyramid Blending on CPU               | 95 |

| 9.7  | Performance of Unsharp Mask on CPU                   | 95 |

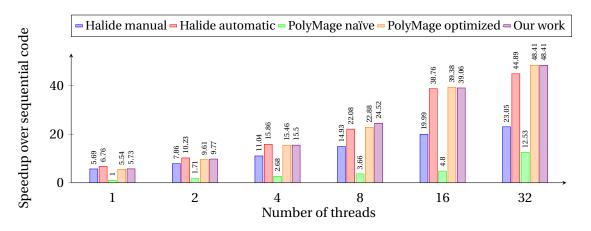

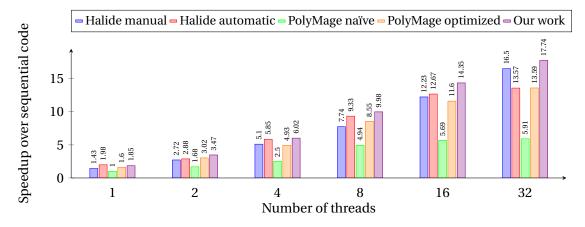

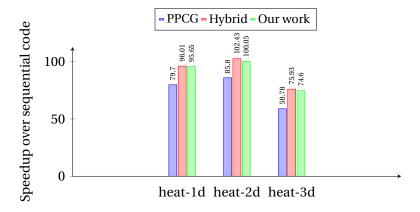

| 9.8  | Performance of heat-1d stencil on CPU                | 97 |

| 9.9  | Performance of heat-2d stencil on CPU                | 97 |

| 9.10 | Performance of heat-3d stencil on CPU                | 97 |

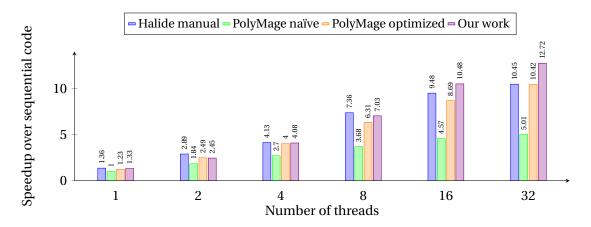

| 9.11 | Performance of the PolyMage benchmarks on GPU        | 98 |

| 9.12 | Performance of the iterated stencils on GPU          | 99 |

# **List of Tables**

| 1.1 | The memory hierarchy of NVIDIA Tesla GPUs in the past five years | 6  |

|-----|------------------------------------------------------------------|----|

| 1.2 | List of xPUs used for AI Accelerators                            | 7  |

| 6.1 | Summary of the input sparse matrices                             | 62 |

| 9.1 | Summary of the PolyMage benchmark                                | 90 |

| 9.2 | Problem sizes and tile sizes of the iterated stencils            | 96 |

# PART I

INTRODUCTION & BACKGROUND

# Introduction

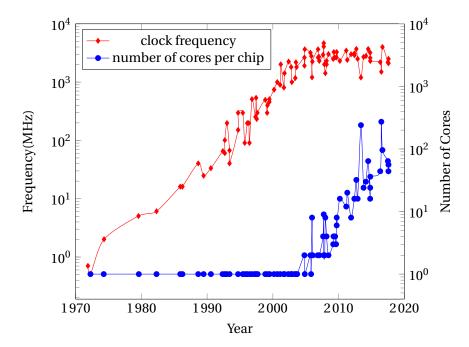

In the early stage of high-performance computing, increasing clock frequencies was the main source of performance gain. Since the breakdown of Dennard scaling a dozen years ago, most CPU manufacturers have been focusing on multicore processors as an alternative of raising clock frequencies from one generation to next. Figure 1.1 shows the semi-centennial trend of clock frequency and number of cores per chip.

Multicore processors are nowadays ubiquitous on almost all platforms, ranging from super-computers ranked on the TOP500 list to personal laptops and mobile devices. In addition, their pervasiveness in the embedding computing domain of multimedia and image processing due to the recent process of neural networks also validates the dominance of multicore processors in all realms of computing.

Figure 1.1 - The trend of clock frequency and number of cores per chip in the past 50 years

Apart from the resulting improvements in performance due to the introduction of multicore processors, one of the most challenging issues is the difficulty to effectively exploit parallelism on such devices. On the one hand, a multicore processor is allowed to implement multiprocessing freely by coupling the cores on the device either tightly or loosely, leading to a variety of memory hierarchies and resulting in the diversity in architectures. On the other hand, the evolution of parallel architectures also calls for the innovation of programming languages amenable to the memory hierarchy, giving rise to the design of both general-purpose and domain-specific parallel programming languages and complicating the programmability issue further.

Even though end users may be equipped with the knowledge of the high-level programming language of a platform after a long-term study or training, it is still a complex and error-prone task to deploy the code written by end users on the target architecture. An optimizing compiler is not only responsible for translating the code implemented by a high-level general-purpose/domain-specific language into a low-level executable program, but is also expected to automatically apply both high-level and low-level transformations, especially those performance-critical loop transformations, for exploiting parallelism and improving locality, thus releasing the burden of end users from taking the hardware information into consideration at the beginning of programming.

In the domain of scientific and engineering applications, a large number of computationally intensive applications spend most of the execution time on nested loops, making the polyhedral model [FL11] a very competitive and promising approach to solving the above problems. The polyhedral model is a powerful mathematical abstraction of loop nests, providing a way to reason about loop transformations by abstracting each iteration of a statement as an integer point in a "polyhedron" and mapping a multi-dimensional logical execution date [Fea92b] for defining its lexicographic execution order. As a role of bridging the gap between high-level programming interfaces and underlying hardware, the polyhedral model has made a great deal of progress in the past few decades, but it is now facing new emergent challenges brought by both modern architectures and programming languages.

## 1.1 From General-purpose Languages to Domain-specific Languages

Thanks to the significant advances in dependence analysis [Fea91, Pug91, VBCG06, BCVT13], schedule transformation [Fea92a, Fea92b, LL97, BHRS08, BAC16, UC13, ABC18] and code generation [AI91, Che, QRW00, Bas04, VBC06, GVC15], the polyhedral model has been brought to the front scene in automatic parallelization and locality optimization. There exist a large number of mature polyhedral compilation frameworks and loop optimizers, including both research projects [BHRS08, CCH08, VCJC+13] and commercial productions [TCE+10, GGL12, CSG+05, BGDR10, LLS06]. Such compilers usually take a general-purpose (intermediate) language as input and generate optimized high-level/low-level code amenable to the target architecture as demand. Despite that, the optimality of the code generated by such polyhedral

compilers still remains elusive, falling behind the performance of heavily hand-tuned codes written by an expert.

Part of the reason of performance gap between the generated codes of optimizing compilers and hand-written programs is due to the conservativeness that a compiler has to possess in nature as system software, reducing the optimization space of automatic transformations. Worse yet, the absence of the ability to reason about the domain knowledge about the implementation strategies from a piece of code also constraints such compilers, missing aggressive and/or global optimizations that can be performed by hand.

Domain-specific languages (DSLs) are proposed to obtain high performance and now very prevalent in many application domains. The polyhedral model was successfully integrated with DSLs, such as those for optimizing DSLs for graphical dataflow language [BB13, SSPS16], stencil computations [HVF+13], etc. Recently, due to the revolution in machine learning caused by the success of deep learning, the polyhedral community is also expected to resolve the problem of bridging neural network applications and high-performance hardware accelerators. A DSL may be a standalone language or more often embedded in a general-purpose language, like Halide [RKBA+13] in C++, TensorComprehensions [VZT+18] and TVM [CMJ+18] in Python<sup>1</sup>, DeepDSL [ZHC17] in Scala, etc. A domain-specific compiler leverages specialized internal representations for expressing domain-specific knowledge, extending its optimization space by enabling such domain-specific high-level transformations. Representative DSL compilers for such applications include the TensorComprehension framework for automating the deployment of neural network applications on multicore platforms and the PolyMage compiler [MVB15, MAS+16] for Halide [RKBA+13], a DSL for writing high-performance image processing code.

While the polyhedral model eases the translation of both general-purpose languages and DSLs on modern architectures, it often suffers from scalability challenges to various input languages. Even though some internal representations like Hailde IR and PENCIL [BBC<sup>+</sup>15] were proposed as the solution to this problem, the polyhedral model still faces many painful problems due to its incompetence for dynamic control and non-affine applications.

## 1.2 Architecture Diversity

Generally speaking, a multicore system is supposed as homogeneous if the system includes only identical cores, or heterogeneous otherwise. The Pluto optimizer [BHRS08] provides a systematic, end-to-end way for automatic parallelization and locality optimization on homogeneous multicore systems, taking into consideration the memory hierarchy problem by automating simply/complex tile shapes [BBP17]. The emergence of Graphics Processing Units (GPUs) brought new challenges not found in homogeneous systems to the polyhedral model, calling for source-to-source polyhedral compilers capable of generating correct codes for both

$<sup>^{1}</sup>$ TensorComprehensions and TVM here are used to refer to the DSLs rather than the compiler stacks.

host processors and device accelerators, further complicating the code generation issue.

Unlike CPUs that can run efficiently when data is resident in Caches, GPUs have a variety of different kinds of processing units, leading to a more complicated memory hierarchy. For instance, Table 1.1 lists the memory hierarchy of fastest NVIDIA Tesla GPUs in the past five years.

| Tesla Product          | Tesla K40      | Tesla M40       | Tesla P100     | Tesla V100    |

|------------------------|----------------|-----------------|----------------|---------------|

| GPU                    | GK180 (Kepler) | GM200 (Maxwell) | GP100 (Pascal) | GV100 (Volta) |

| Memory Size            | Up to 12 GB    | Up to 24 GB     | 16 GB          | 16 GB         |

| L2 Cache Size          | 1536 KB        | 3072 KB         | 4096 KB        | 6144 KB       |

| Shared Memory Size     | 16/32/48 KB    | 96 KB           | 64 KB          | 96 KB*        |

| Register File Size/SM  | 256 KB         | 256 KB          | 256 KB         | 256 KB        |

| Register File Size/GPU | 3840 KB        | 6144 KB         | 14336 KB       | 20480 Kb      |

Table 1.1 – The memory hierarchy of NVIDIA Tesla GPUs in the past five years

PPCG [VCJC<sup>+</sup>13] is considered as one of the most successful polyhedral compilers for heterogeneous systems, exploiting parallelism and locality optimization as in traditional homogeneous systems but also automating the management of memory system on devices and communications between host and device. Like the diamond tiling technique in Pluto, a hybrid/hexagonal tiling approach [GCH<sup>+</sup>14] is also implemented in PPCG for further improving the performance of generated code. Some follow-up PPCG-based researches focus on parametric tiling [JGTC14] and the mapping and separation of multi-level parallelisms in the accelerators of a heterogeneous system [SHS17].

Besides shared memory strategy, message passing is also used as the inter-core communication method in distributed systems and heterogeneous systems, requiring the code generator of an optimizing compiler to express the explicit communication with libraries like Message Passing Interface (MPI). Polyhedral compilation frameworks targeting on minimizing communication volume [Bon13, RB14] or handling the mixture of regular/irregular loop nests [RDE+15] were proposed for such multicore systems.

Similarly, accelerators in heterogeneous systems are not restricted to GPUs. For example, configurable devices like Field-Programmable Gate Array (FPGA) [BRS07, PZSC13] can also be the target of an optimizing compiler, followed by some researches in high-level synthesis area [ZLC+13, WLC14]. These together with the above mentioned architectures are calling for a strict portability of the polyhedral model to multiple platforms. Recent work integrating multicore parallelism and Single Instruction Multiple Data (SIMD) vectorization [TNC+09, KVS+13] not only addressed the code generation issue but also implemented a different

$<sup>^{*}</sup>$  The shared memory size of GV100 (Volta) is confinable up to 96 KB.

scheduling strategy in a tile.

Even though the advances made by the polyhedral community on so many accelerators, there still exits a long way to achieving architectural portability. The emergence of artificial intelligence applications has brought new challenges for this issue. For instance, Table 1.2 summarizes the latest xPUs used for modern artificial intelligence accelerators.

Abbreviation Full name Manufacturer Released year **APU Accelerated Processing Unit AMD** 2011 **BPU Brain Processing Unit Horizon Robotics** 2017 Deep Learning Processing Unit Deephi Tech 2016 DPU **Dataflow Processing Unit Wave Computing** 2017 **EPU Emotion Processing Unit Emoshape** 2017 **HPU** Holographic Processing Unit Microsoft 2017 **Intelligence Processing Unit** GraphCore 2017 **IPU Intelligence Processing Unit** Mythic 2018 **Image Processing Unit** Google 2017 **NPU Neural Network Processing Unit** Vimicro 2016 **SPU** Stream Processing Unit **AMD** 2006 **TPU Tensor Processing Unit** Google 2016 **VPU** Vision Processing Unit Intel 2016 **ZPU** Zylin CPU Zylin AS 2015

Table 1.2 - List of xPUs used for AI Accelerators

### 1.3 Beyond Parallelization and Locality Optimization

On modern multicore processors, parallelism due to the increased core numbers on a single chip and locality caused by memory hierarchy are the two main objectives considered by compiler designers. As a result, optimizing compilers like a polyhedral optimizer are usually expected to be capable of automatic parallelization and locality optimization. Unfortunately, parallelization and locality optimization are sometimes contradictory with each other by putting conflict constraints on the objective function of scheduling algorithms, forcing them to make a tradeoff between parallelism and locality for achieving optimality of performance.

As a loop transformation aiming at improving locality while preserving the parallelism that has been exploited by a scheduling algorithm, loop tiling [IT88] has been long considered as foreign to optimizing compilers; even for the polyhedral model, it could not be easily expressed using an affine function a decade ago. Thanks to its recent advances, the polyhedral model has been proved to be promising in automating loop tiling. A cost-model-based scheduling

algorithm like the Pluto scheduler [BHRS08] or its variants put into practice the automation of simple tile shapes in the polyhedral model. A follow-up trend on the automatic tiling technique focuses on more complex tile shapes like diamond [BBP17] and hexagonal [GCH<sup>+</sup>14] working with arbitrary affine dependences, and overlapped and split shapes [KBB<sup>+</sup>07] restricted to constant dependence vectors.

Loop fusion [KA02] is another loop transformation to enhance locality and reduce synchronizations across multiple loop nests. There have also been successful advances on loop fusion in the polyhedral model [BGDR10, MLY14, JB18], providing a variety of fusion heuristics to modern optimizers.

Storage optimization is also a research direction of polyhedral compilation. Array contraction, for example, is a long considered automatic memory footprint optimization in the polyhedral world. The applicable domain is still constrained to special cases like stencil computations although researchers made a lot of efforts in this direction, including the universal-occupancy-vector-based [SCFS98], lattice-based [DSV05] and storage-hyperplane-based [BBC16] techniques, etc.

In spite of the exciting progresses made by the polyhedral community on automatic parallelization and locality optimization, there still exist a large number of opening issues awaiting supports and efforts. The latest research trend also tried to integrate the polyhedral model with dynamic/runtime techniques [KPP+15, SRC15, BKP+16, SPR17] for extending the scope of the tool, leaving much room for the extensions in this field.

## 1.4 Combining Languages and the Polyhedral Model

The polyhedral model so far is successful in so-called "static control parts" (SCoPs) where loop nests satisfy certain statically predictable restrictions. There is an increasingly emergent demand on its applicability to non-affine domains to cope with the complexity of modern multicore architectures. A notable direction among the open challenges is the incompetence of the polyhedral model to handle non-affine applications and transformations. Such non-affine applications usually involve dynamic data-dependent control flow and/or non-affine expressions that go beyond the scope of the polyhedral model, while non-affine transformations<sup>2</sup> are usually not expressible using existing techniques.

A representative polyhedral-based approach on non-affine applications are the work of handling while loops [BPCB10], along with a great deal of work with special focus on sparse matrix computations [SGO13, VSHS14, VHS15, SLC+16, VMP+16]. The former misses more aggressive optimizations when handling less expressive dynamic conditions than a general while loop, while an inspector/executor scheme is usually constrained to a subset of sparse matrix computations.

$<sup>^2</sup>$ An affine transformation should be "signle-valued", i.e., an one-to-one mapping function of the integer points on iteration space.

With regard to non-affine transformations, overlapped tiling [KBB+07] is a representative technique gaining much attentions recently due to its compatibility with other optimizations like fusion, scratchpad memory allocation, etc. when optimizing image processing pipelines. Unlike a standard tile shape exploited by current polyhedral compilers, additional overlapped regions are introduced for exploiting inter-tile parallelism in such transformation by jointing consecutive tiles. Unfortunately, no implementations of overlapped tiling in a general-purpose polyhedral framework have been reported except PolyMage [MVB15], a DSL compiler for image processing pipelines.

This dissertation describes a combined language and polyhedral approach to extend the application domain of the polyhedral model in non-affine applications and express non-affine transformations in the model. On the one hand, we study the parallelizing compilation and loop nest optimization of an important class of programs where counted loops have a dynamic data-dependent upper bound. Such loops are amenable to a wider set of transformations than general while loops with inductively defined termination conditions: for example, the substitution of closed forms for induction variables remains applicable, removing the loop-carried data dependences induced by termination conditions; such loops can also be viewed a generalization of sparse matrix computations using compressed data layout stores nonzero elements only as the latter can be easily generalized by subtracting the lower bound from the upper bound.

On the other hand, we revisit overlapped tiling in polyhedral compilation and demonstrate how to derive tighter tile shapes with less redundant computations, by enabling overlapped tiles based on a well-defined general-purpose intermediate representation. It releases the overlapped tiling in polyhedral model from being restricted to a domain-specific language while not introducing sophisticated rescheduling and custom code generation in a polyhedral framework.

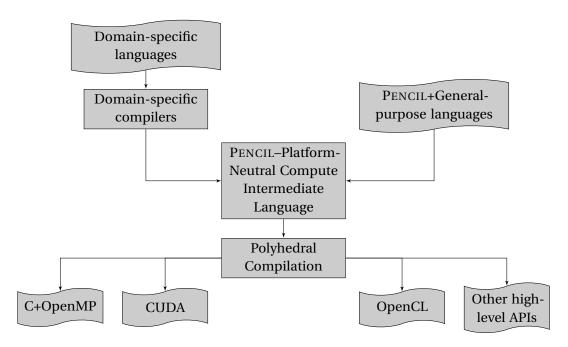

Given the diversity of multicore architectures and the difficulty of programming on these platforms, a polyhedral compilation approach has become a compelling alternative for writing parallel code on these targets. Our approach is driven by combining an intermediate language and the polyhedral model, not only removing the conservativeness caused by using a general-purpose language hindered by the difficulty of static analysis but also avoiding the implementation of a DSL compiler for the portability to different architectures. By coupling with such an intermediate language, one may define coding rules predominantly related to restricting the non-statically predictable manners, allowing for better optimizations when translating such programs into the code on target machines using a polyhedral framework. More importantly, leveraging such an intermediate language also eases the code generation for different architectures, making the portability issue a straightforward task.

Our method on counted loops with a dynamic data-dependent upper bound goes beyond the state of the art in fully automating the process, specializing the code generation algorithm to the case of dynamic counted loops and avoiding the introduction of spurious loop-carried

#### **Chapter 1. Introduction**

dependences. The experimental results on representative irregular computations ranging from dynamic programming, computer vision and finite element methods to sparse matrix linear algebra validate that the method is applicable to general affine transformations for locality optimization, vectorization and parallelization.

Our algorithm to generalize overlapped tiling allows for tighter overlapped tile shapes than the state of the art, further improving the performance of image pipelines on both general-purpose multicores and heterogeneous accelerators by integrating with transformations including alignment and scaling of stages in the pipeline, loop fusion, scratchpad allocation, hybrid tiling, etc. The experimental evaluation on the PolyMage benchmarks and representative iterated stencils validates the effectiveness and general applicability of our technique on both general-purpose multicores and accelerators.

The organization of the dissertation is as follows. In the first part, we described in this chapter an introduction to the problem we aim at in this dissertation, followed by Chapter 2 providing the technical background on the polyhedral model and the intermediate language used in our approach. The second part presents our method to handle non-affine application, i.e., parallelization and optimization of counted loops with a dynamic data-dependent upper bound, including the motivation and related work in Chapter 3, scheduling algorithm in Chapter 4, code generation method in Chapter 5 and experimental results in Chapter 6. Generalizing overlapped tiling in the polyhedral model regarding the non-affine transformations is introduced in the third part, comprising Chapter 7 describing the motivation and related work, Chapter 8 explaining the polyhedral implementation of the method and Chapter 9 evaluating the proposed technique on both homogeneous and heterogeneous architectures. We finally conclude the dissertation in the last part, Chapter 10, by summarizing the topics studied in the dissertation and discussing directions for further research.

# 2 Background

After a thirty-year evolution, the polyhedral model has become a powerful optimizer in the domain of automatic parallelization and optimization. There have been a great number of open-source and/or commercial implementations of polyhedral compilation in both research and industry worlds. Comparing with unimodular matrices [Ban93, WL91] used in parallelizing compilers, the polyhedral model is equipped with (1) wider range of applications due to the capability to transform imperfect loop nests, (2) more powerful expressiveness by modeling almost each kind of loop transformations and (3) greater optimization space by compositing more transformations at one time.

As a consequence, polyhedral compilation nowadays is gradually becoming the state of the art of almost each domain of parallelizing compilers. In this chapter, we would first introduce the background of polyhedral compilation for a better understanding of the underlying principle of the polyhedral model. To cope with polyhedral compilation for non-affine applications and transformations, we would next present the intermediate language used in the dissertation.

### 2.1 Polyhedral Compilation

As we introduced in the previous section, the polyhedral community so far has made a great deal of progress in all realms of computing. Nonetheless, polyhedral compilation is long considered as too abstract for those people outside the polyhedral world. Part of the reason is due to the painfully theoretical descriptions in existing polyhedral publications; more importantly, the underlying principle of the polyhedral model involves a variety of concepts from linear algebra, static analysis, etc., making the use of the tools elusive for end users.

To make it easier to understand the polyhedral model, we introduce the background of polyhedral compilation in this section. One may refer to [FL11] for a much detailed description on fundamental concepts and definitions. In general, we would first give an overview of modern polyhedral compilation and then explain how programs are represented in the model. Next, the transformations that can be modeled in the polyhedral model are presented by comparing

with conventional methods used in parallelizing compilers, followed by an introduction to a well-defined representation of the polyhedral model.

### 2.1.1 An Overview

The pioneer work of the polyhedral model is the contribution of Karp et al. on systems of uniform recurrence equations [KMW67]. With the development of polyhedral compilation, integer polyhedra [LW97] and Presburger relations [PW94a, PW94c] were also introduced into the model for better expressiveness and flexibility purpose. Polyhedral compilation can either be integrated as a building block into a general-purpose compiler, e.g., Polly in LLVM, or serve as a standalone source-to-source translator like Pluto and PPCG. Such flexibility and compatibility help itself construct a well-defined compilation workflow and extend its application domain to a great extent.

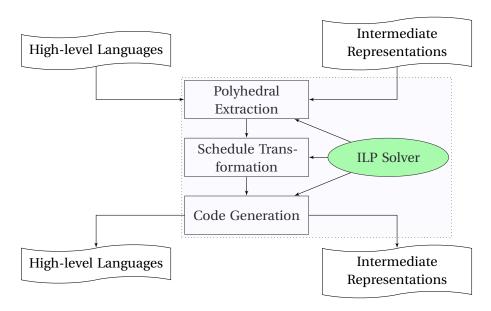

To date, polyhedral compilation has reached maturity and emerged into a fully fledged work-flow. Figure 2.1 shows a general compilation workflow of modern polyhedral compilers. Polyhedral compilation can either take as input a high-level programming language when serving as a standalone optimizer or an intermediate representation when embedded in a general-purpose compiler. With regard to generated code, a high-level language wrapping parallel programming APIs executable on target platforms can be generated; otherwise, the optimized intermediate representation of the host compiler would be returned, possibly followed by other transformation passes of the host compiler.

Figure 2.1 – A general workflow of polyhedral compilation

Typically, polyhedral compilation consists of three steps, as the three modules enclosed by the dotted frame in Figure 2.1 show.

**Dependence analysis.** First, polyhedral extraction is serving as the frontend, parsing the code fragment of input languages and extracting polyhedral representations with regard to statement instances and array elements for the program. The duty of a parser is checking whether the input is a "SCoP", meaning the code fragment is statically predictable and polyhedral compilation would represent the input program with finite internal representations if true. pet [VG12] and clan [cla] are two representative, practical parsers for polyhedral compilation, generally used in a variety of mature polyhedral compilers. Such representations of statement instances and their relationships with the array elements they access are used to compute dependence relations by solving an integer linear programming (ILP) problem.

Polyhedral compilation differentiates dependence analysis from conventional methods by refining the analysis from statement-wise to instance-wise [Fea91]. Dependence relations can be further separated into value-based dependences, the result of data flow analysis [MAL93, Mas94], used for preserving the semantic of programs, and memory-based dependences, studied for the purpose of improving data reuse [PW92, VBCG06, BCVT13].

**Schedule transformation.** Secondly, schedule transformation is the core of polyhedral compilation, producing a new schedule by taking into consideration target architectures. In other words, schedule transformation is the process of mapping a new logical execution date for each integer point in a polyhedron, accomplished by invoking the underlying ILP solver. The process of schedule transformation could also be considered as a composition of different loop transformations with the purpose to fully exploit parallelism and data locality.

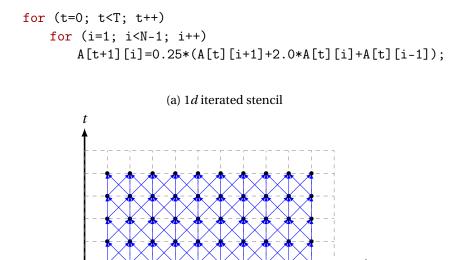

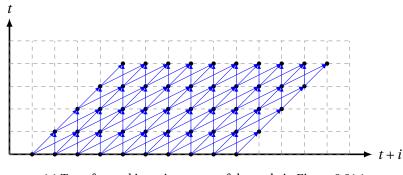

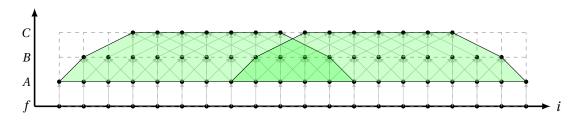

We take the 1D iterated stencil shown in Figure 2.2(a) as an illustrative example. Iterated stencils are a class of computations updating an array element using its neighbors, commonly found in computational fluid dynamics, image processing, partial differential equations, etc. The original iteration space of the 1D stencil code is shown in Figure 2.2(b), indicating the computation proceed first along t axis and then t axis. Instead, the transformed iteration space after schedule transformation in Figure 2.2(c) implies the computation should first follow t axis and then t+i axis. The instances of the statement are represented by integer points in iteration space, coordinated with each other by a blue arrow denoting a dependence relation.

Tiling along t axis and i axis in Figure 2.2(b) is illegal since such tiling may produce dependence cycles between tiles along i axis, prohibiting the data locality along t axis of the original iteration space. On the contrary, one may benefit from the data locality along both axes on the transformed iteration space as tiling along the axes may not result in dependence conflicts. In fact, schedule transformation could be understood as the reconstruction of the basis of iteration space, attained by a scheduling algorithm like [Fea92a, Fea92b, LL97, BHRS08, BAC16, UC13, ABC18] and their variants in libraries. While the scheduling algorithm proposed by Feautrier [Fea92a, Fea92b] was complained due to the missing of considering communication

(c) Transformed iteration space of the code in Figure 2.2(a)

Figure 2.2 – 1D iterated stencil and its iteration space before and after scheduling

overhead, the hyperplane<sup>1</sup> partitioning technique [LL97] also failed to minimize the order of synchronization even though it takes into account communications. The cost-model-based scheduler [BHRS08] developed in the Pluto compiler was designed to overcome such flaws and has been demonstrated as effective in practice by a variety of implementations.

Schedule transformation is considered as the most difficult component of polyhedral compilation. A scheduling algorithm is tightly coupled with dependence relations produced by the frontend: while it should preserve the semantic of the program by being constrained to dependence relations, it is also expected to minimize dependence distances for reuse purposes, thereby improving data locality. A scheduling algorithm is not only responsible for exploiting different compositions of loop transformations, e.g., the composition of loop tiling and skewing could be triggered in the example of Figure 2.2, but also obligated to exploit both fine-grained and coarse-grained parallelisms. Moreover, a scheduling algorithm should

$<sup>^{1}</sup>$ A hyperplane is the projection of an n dimensional space on its n-1 dimensional sub-space.

also take into consideration the requirements from follow-up code generation: for example, schedule transformation should allow the insert of thread-/warp<sup>2</sup>-level synchronizations when generating CUDA code on GPUs.

**Code generation.** Finally, code generation constitutes the backend of polyhedral compilation, made up by two phases with one building abstract syntax trees (ASTs) from the results of polyhedral extraction and schedule transformation while the other generating expected high-performance code executable on target platforms. As code generation would not change the execution order of programs, it is allowed to not take into consideration dependence relations, scanning the iteration space and generating code according to execution dates defined by the transformed schedule. As a consequence, code generation is also referred to as polyhedral scanning.

When building ASTs from the results of previous steps, a code generator manages to determine loop bounds and conditionals of control flow by seeking solutions for an optimization problem subject to integers. The generated ASTs could then be passed to emit instructions amenable to different programming models on target machines, facilitating the portability to different architectures.

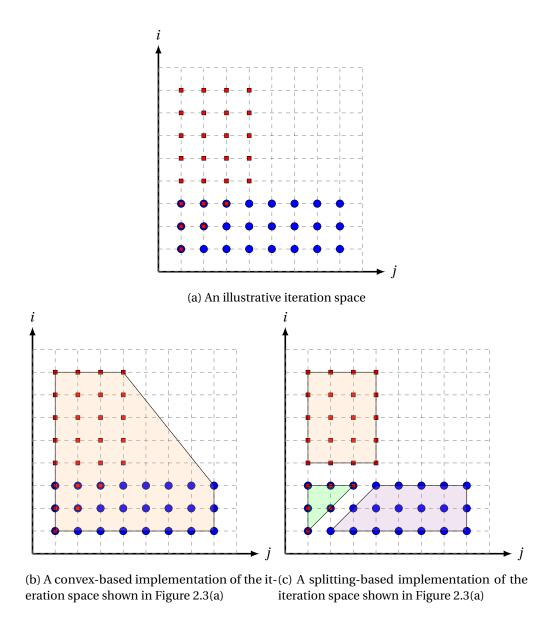

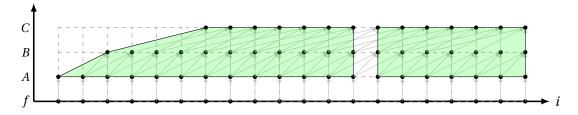

One representative implementation of code generation in polyhedral compilation is the convex-based algorithm [AI91], generating code by first constructing a convex for all polyhedra in the iteration space. Figure 2.3(a) shows an illustrative iteration space composed of two polyhedra with one comprising all red square points and the other made of blue circle points, followed by a diagram of convex-based algorithm in Figure 2.3(b). One of the flaws of this algorithm is the generated code may include multiple nested if conditionals governing the correct execution of each polyhedron in the iteration space, promoting some code generators like Codegen+ working on hoisting if conditionals [Che]. The other code generation technique was proposed by Quilleré et al. [QRW00] and implemented in the CLooG generator and its variants [Bas04, VBC06, GVC15]. Unlike the convex-based algorithm, the method used in CLooG may first split the polyhedra into distinct regions as shown in Figure 2.3(c), producing code by scanning each of such regions individually.

As one may also find in Figure 2.1, an ILP solver is at the core of polyhedral compilation, providing each step with minimal flexible integer solutions, thereby achieving the manipulation of polyhedral transformations. There exist a variety of libraries for solving ILP, including isl [Ver10], Omega [KMP+96], PIP [Fea88], PolyLib [Loe99] and PPL [BHZ08], etc., differing each other by using different algorithms and data structures.

<sup>&</sup>lt;sup>2</sup>A warp is a set of threads arranged lengthwise on a loom and crossed by the woof.

Figure 2.3 – An illustrative diagram on different code generation algorithms

### 2.1.2 Polyhedral Representations

Intuitively, polyhedral compilation models one statement in loop nests as a polyhedron and each instance of the statement as an integer point. One may understand those transformations enabled by polyhedral compilation as the process of reshaping such polyhedra. In terms of implementing the polyhedral model in a parallelizing compiler, however, one may have to resort to some polyhedral representations for both manipulation and optimization purposes. Historically, there have been various compositions of different representations used in polyhedral compilation, but we would like to introduce the following representations used in the dissertation as they are sufficient to model polyhedra and have been implemented in

some widely used optimizers like LLVM/Polly, PPCG, etc. One is without doubt free to choose any other combinations of representations for their implementation, as such representations could always be mutually transformed.

Before the introduction to polyhedral representations, we prefer to first present some mathematical concepts. This is because such mathematical concepts are the underlying expressions in integer manipulation libraries. More importantly, it would be a painful task to explain polyhedral representations if bypassing such mathematical concepts. If the readers are interested in a more detailed description or some more concentrated examples on such mathematical descriptions, we would suggest to refer to the work of Grosser [Gro14].

**Integer sets.** An integer set is a set of n-tuple integers subject to a group of affine constraints relating such n-tuple integers with m-tuple constant parameters, with n representing the dimensionality of the set, m the dimensionality of the parameters in constraints. Mathematically, an integer set can be written as

$$S = \{(i_1, i_2, ..., i_n) : f((i_1, i_2, ..., i_n), (p_1, p_2, ..., p_m))\}$$

(2.1)

An integer set is called named integer set when assigning a name to the integer tuple. In practice, one may think an n-tuple integer set as the collection of loop iterators, m-tuple constant parameters the parameters of programs. A constraint function usually comes as the conjunction of multiple inequalities.

**Integer maps.** An integer map is a binary relation mapping an  $n_1$ -dimensional integer set, i.e., the domain of the map, to another  $n_2$ -dimensional integer set, i.e., the range of the map, subject to a set of affine constraints on the integer sets and constant parameters. An integer map can be generalized as

$$M = \{(i_1, i_2, ..., i_{n_1}) \rightarrow (i_1, i_2, ..., i_{n_2}) : f((i_1, i_2, ..., i_{n_1}), (i_1, i_2, ..., i_{n_2}), (p_1, p_2, ..., p_m))\}$$

(2.2)

An integer map can be interpreted as the relation between statement instances with their accessed data locations or dependence relations. In the same way, a named integer map represents an integer map between two named integer tuples.

**Named union sets and Named union maps.** We use named union sets to refer to the union of different named integer sets, and named union maps for the union of different named integer maps. Named union sets can be used to express all statement instances of a SCoP,

while named union maps may either define execution order on statement instances or relate statements and the data they access.

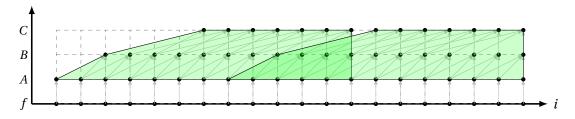

Given the above mathematical concepts, we can explain polyhedral representations in a much easier way. Following the previous subsection, we still use an illustrative example for explanation. One may obtain the iteration space of the loop nest listed in Figure 2.4(a) as shown in Figure 2.4(b), with one polyhedron for statement S1, composed of blue points, and the other for statement S2, depicted with the collection of all red points. f and g are affine functions of their indices. In our work, we would use the following representations.

```

for (i=1; i<=4; i++) {

S1: a[i] = f(i);

for (j=1; j<=i; j++)

S2: b[i][j]=g(a[i]);

}

(b) The iteration space of the loop nest shown in Figure 2.4(a)

```

Figure 2.4 – An illustrative loop nest and its iteration space in polyhedral compilation

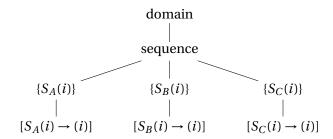

**Iteration Domain.** Iteration domain is the collection of all statement instances, represented using a named union set with each named component covering all instances of one statement followed by a set of inequalities for bounds. The iteration domain of the code above can be expressed with (2.3).

$$Domain = \{S_1(i) : 1 \le i \le 4; S_2(i, j) : 1 \le i \le 4 \land 1 \le j \le i\}$$

(2.3)

Access Relations. Access relations are a set of relations coordinating statement instances with the data locations they access, modeled by a set of named union maps together with some inequalities for bounds. (2.4) describes the access relations of the example, consisting of a Write relation and a Read relation. By refining access relations with read and write relations, polyhedral compilation is free to compute dependence relations easily. Furthermore, a write relation can also be split into may-write and must-write relations for the purpose of aggressive optimizations.

$$Write = \{S_1(i) \to a(i) : 1 \le i \le 4; S_2(i, j) \to b(i, j) : 1 \le i \le 4 \land 1 \le j \le i\}$$

$$Read = \{S_2(i, j) \to a(i) : 1 \le i \le 4 \land 1 \le j \le i\}$$

(2.4)

**Schedule.** As we already mentioned in previous context, polyhedral compilation would map a multi-dimensional logical execution date to each statement instance. Schedule is such a multi-dimensional execution date assigned to a statement instance, expressed using a binary relation between two different multi-dimensional integer tuples. A lexicographically smaller schedule implies an earlier execution of the statement instance. An original schedule is the execution date assigned to a statement instance before schedule transformation. For example, the original schedule of the code in Figure 2.4(a) can be written as (2.5). A new schedule would be computed after schedule transformation if the scheduling algorithm may find a better execution date with respect to parallelism and data locality.

$$Schedule = \{S_1(i) \to (i,0); S_2(i,j) \to (i,1,j)\}$$

(2.5)

**Dependences.** Dependences represent the access conflicts between statement instances, written as named union maps and used for guaranteeing the execution date of a producer be lexicographically smaller than that of the consumer, therefore enforcing the correctness of any transformations enabled by polyhedral compilation. A refinement from traditional statement-level dependences to instance-level dependences in the polyhedral model makes the expression of dependences more complicated, like the constraints after the named maps shown in (2.6) indicating the dependences are described with regard to statement instances.

$$Dependence = \{S_1(i) \to S_2(i,j) : 1 \le i \le 4 \land 1 \le j \le i\}$$

(2.6)

#### 2.1.3 Loop Transformations

Given the polyhedral representations, one may apply any loop transformations and/or their compositions. Loop transformations could be attained by schedule transformations, i.e., reordering the statement instances. Considering the example shown in Figure 2.2, schedule transformation triggers loop skewing by specifying a new execution date to the statement instances of 1D iterated stencil.

If we use the polyhedral representations introduced in the last subsection to express the transformation, we may obtain the original schedule as  $\{S_1(t,i) \to (t,i)\}$  and  $\{S_1(t,i) \to (t,t+i)\}$  for the new schedule after applying loop skewing. As a result, a transformation could be

expressed as  $(t, i) \to (t, t+i)$  for representing loop skewing. Suppose t and i as variables, the underlying principle of schedule transformation could be interpreted as seeking a coefficient matrix and a constant vector such that

$$\begin{bmatrix} c_{11} & c_{12} \\ c_{21} & c_{22} \end{bmatrix} \begin{bmatrix} t \\ i \end{bmatrix} + \begin{bmatrix} c_{10} \\ c_{20} \end{bmatrix} = \begin{bmatrix} t \\ t+i \end{bmatrix}$$

$$(2.7)$$

It is straightforward to solve the above system of linear equations by hand as the problem is heavily simplified for the sake of illustration. However, polyhedral compilation may have to solve it automatically by resorting to an ILP solver; worse yet, the practical problems faced by the polyhedral model would be much more complicated. We would not go further into the underlying structure of schedule transformation but invent the readers to refer to the work of Bondhugula [Bon08] for a detailed mathematical explanation.

To generalize, schedule transformation can be understood as solving a coefficient matrix and a constant vector such that a transformation between two integer tuples can be accomplished. Each row of the coefficient matrix can be interpreted as a hyperplane. Note that the two integer tuples could differ with regard to dimensionality: for example, a scalar dimension could be introduced to achieve loop fusion. Besides, a more complex example of loop transformation would be loop tiling, increasing the dimension of the input tuple by doubling those components requiring tiling.

Schedule transformation by manipulating integer sets broadens the optimization space of polyhedral compilation and simplifies the composition of different loop transformations compared with traditional compilation models like unimodular matrices [Ban93, WL91], while the latter applies loop transformations by means of elementary matrix operations. Besides, the loop transformations covered by unimodular matrices are also very restricted, including loop interchange, skewing and reversal; the polyhedral model is rather capable for automating a wider set of loop transformations, widening the optimization space by enabling loop fission, fusion, index set splitting [GFL00], peeling, strip-mining [KP95], tiling, unroll and jam [Bon08, BF03], unrolling, unswitching, etc.<sup>3</sup> A recent work [YGK+13] also makes it possible to model algorithmic changes which could not be achieved by other techniques, further enriching the transformations of polyhedral compilation.

#### 2.1.4 Schedule Trees

Apart from index set splitting, all the loop transformations modeled by polyhedral compilation could be facilitated by operating on the schedule representation, i.e., named union maps.

<sup>&</sup>lt;sup>3</sup>Some of these loop transformations, i.e., loop peeling, unrolling, unswitching, are achieved by code generation rather than schedule transformation, since these transformations change the loop structure rather than reorder statement instances.

This, however, does not mean the operations on named union maps would be ease of use. A typical drawback of such method can be found when comparing the lexicographic order of two integer sets, since such operations can only be applied on integer sets with the same dimension.

More importantly, the above mentioned schedule representation could not be easily extended to handle non-affine transformations as named union maps hold the "injectivity" and "single-valuedness" properties. "injectivity" indicates a schedule representation allows different statement instances to be assigned the same logical execution date for expressing inner parallelism; "single-valuedness" refers to a schedule representation would only assign a single execution date to a statement instance, preventing the statement instance from being executed more than once. Clearly, the latter would not allow the implementation of non-affine transformations like overlapped tiling requiring multiple executions of a statement instance.

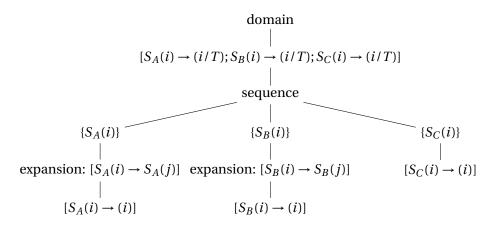

In this dissertation, we rely on a well-defined schedule representation that would make the expression of non-affine transformations possible in polyhedral compilation. As the schedule construction may decompose a dependence graph recursively and compute a partial schedule for each component independently, a schedule representation would naturally have the form of a tree [GVC15]. The schedule representation is thus called "schedule tree".

There have been some schedule representations proposed in the past, including the Kelly's abstraction [KPR95], "2d+1"-schedules [GVB+06], etc., that can be viewed as an encoding of schedule trees. Like named union maps, such encoding methods are usually restricted due to missing the ability to facilitate non-affine applications and transformations.

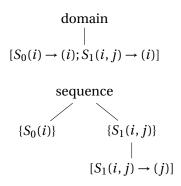

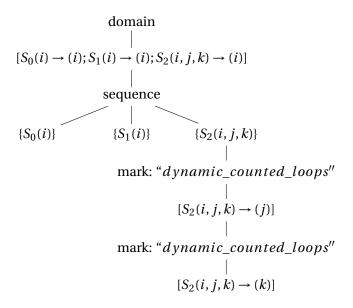

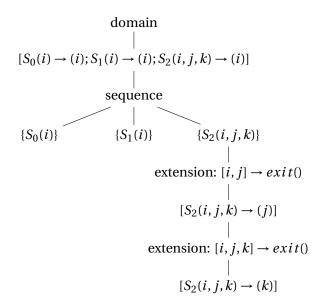

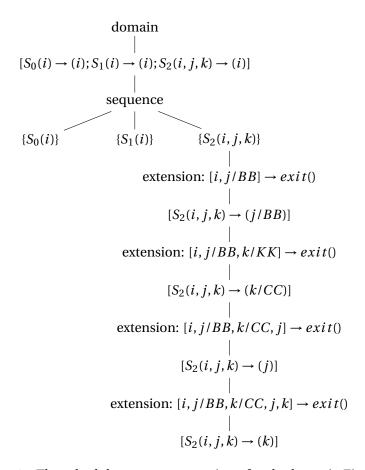

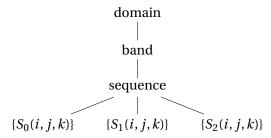

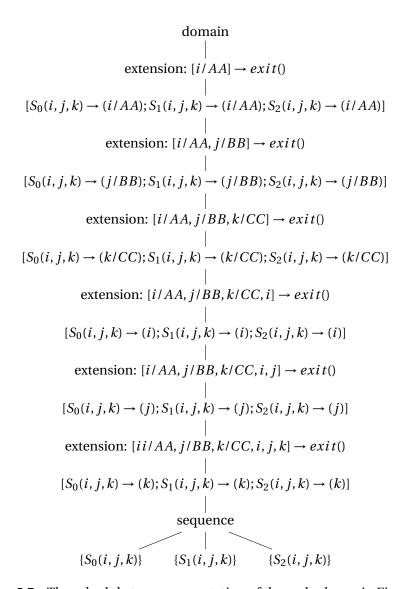

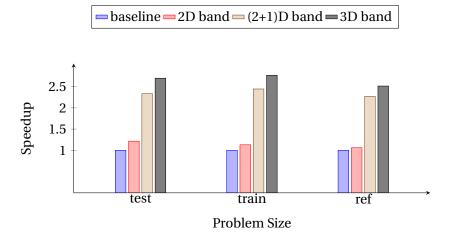

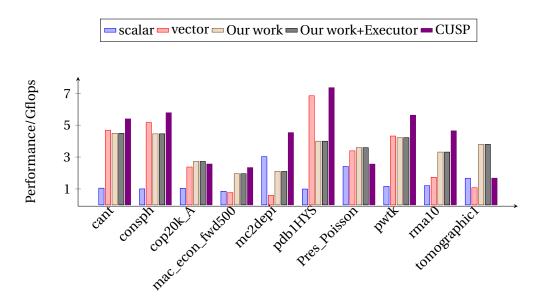

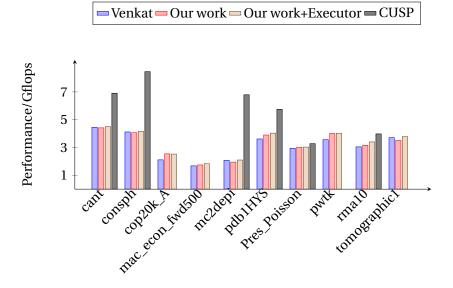

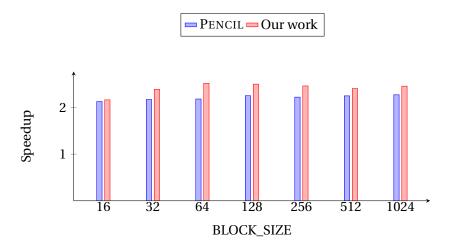

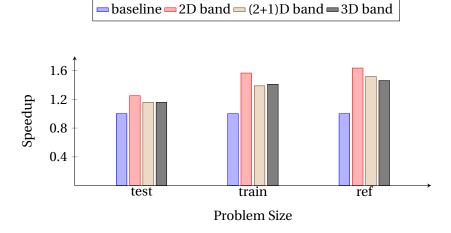

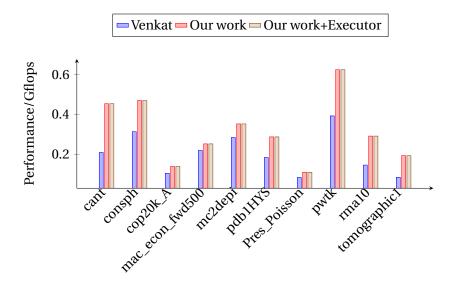

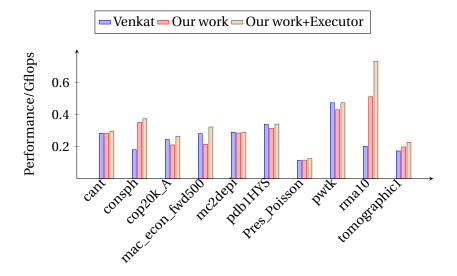

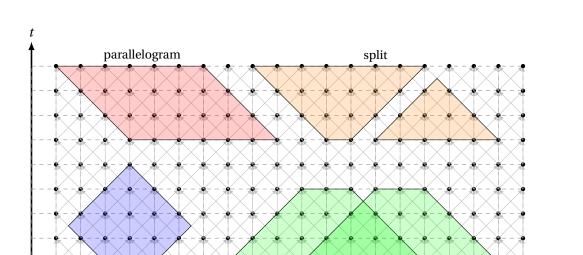

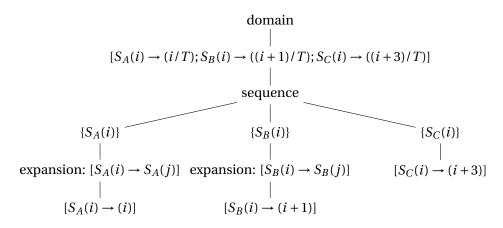

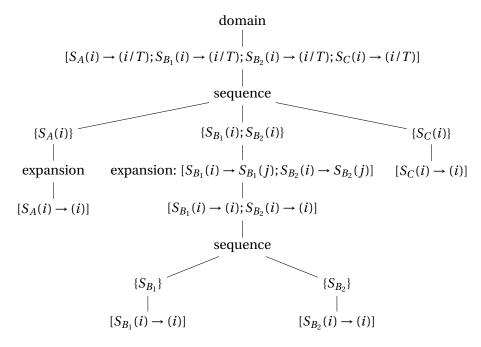

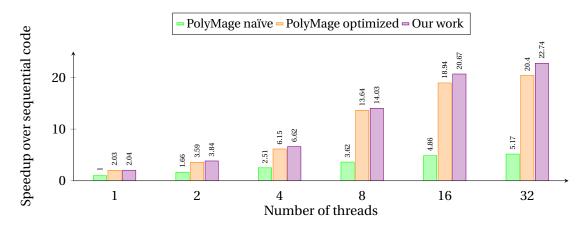

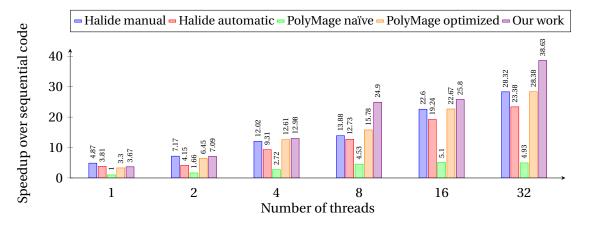

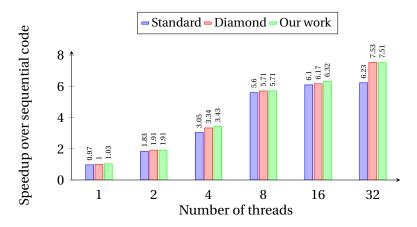

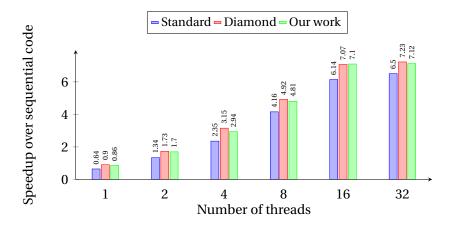

To give an intuitive impression on schedule trees, we depict the schedule tree representation of the code shown in Figure 2.4(a) in Figure 2.5. A schedule tree is constructed by recursively building partial schedule trees which in turn constructed by schedule nodes. For example, the schedule tree in the figure is composed of two sub-trees rooted at one filter node representing statement  $S_1(i)$  and the other for statement  $S_2(i,j)$ . A partial schedule tree comprises one or more schedule nodes for expressing different semantics. We would next introduce the basic node types in schedule trees. For a complete description of schedule trees and nodes, please refer to [GVC15].